Flujo de diseño del proyecto DRAC

La síntesis lógica y física detrás del proyecto DRAC se explica ahora a través de un flujo de diseño, que incluye los pasos de los procesadores basados en la arquitectura RISC-V.

DRAC es un proyecto de investigación con el objetivo de producir procesadores RISC-V y diferentes aceleradores tratando de lograr el máximo rendimiento posible minimizando el consumo de energía. Para lograrlo, una correcta selección del proceso tecnológico donde se fabricarán los procesadores es obligatoria, ya que afecta el rendimiento, el consumo de energía y los costos de fabricación. En el proyecto DRAC se han estudiado varias tecnologías, pero la seleccionada es el proceso tecnológico 22 nm FDSOI (22FDX) de Globalfoundries (GF), ya que nos permite apuntar frecuencias de reloj por encima de 1GHz, nos brinda diferentes opciones para reducir el consumo de energía y los costes de fabricación son relativamente bajos.

El proyecto DRAC es una colaboración conjunta entre el Instituto de Microelectrónica de Barcelona, el Centro de Supercomputación de Barcelona, el Instituto Politécnico Nacional (México) y la UPC, entre otras instituciones.

Fuente original: Barcelona Supercomputing Center.

En el proyecto DRAC estamos diseñando SoCs (del inglés System-on-Chip) que incluyen procesadores basados en la arquitectura RISC-V, diferentes aceleradores y un conjunto de bloques analógicos como son un PLL, un SerDes, un ADC y SPADs (del inglés, Phase-Locked Loop, Serializer Deserializer, Analog to Digital Converter y Single Photon Avalanche Diode, respectivamente). De estos bloques analógicos, el PLL y el SerDes permiten aumentar el número de instrucciones ejecutadas por el procesador; el PLL permite aumentar la frecuencia de trabajo mientras que el SerDes habilita comunicaciones más rápidas con las memorias externas. Por otra parte, el ADC permite interactuar con sensores analógicos y los SPADs son una herramienta para poder habilitar la criptografía cuántica.

A la hora de planificar la estrategia de integración de los diferentes elementos del SoC, debe considerarse que trabajaremos con un diseño de señal mixta. Sin embargo, como los circuitos que ocupan más área y los más complejos son los digitales, la estrategia elegida es la DoT (del inglés, Digital On Top). Esto significa que empezaremos a trabajar como si el SoC fuera puramente digital, y a medio camino añadiremos la información de los bloques analógicos que se han diseñado por separado.

Cada bloque analógico se diseña siguiendo el flujo analógico, utilizando la herramienta "virtuoso" de Cadence®. En cambio, los diseños digitales como el procesador o los aceleradores se codifican con lenguaje RTL (del inglés, Register-Transfer Level), que nos permite describir el comportamiento del circuito que queremos diseñar y verificarlo con simulaciones. Una vez estamos seguros de que el circuito diseñado tiene el comportamiento esperado, se necesita traducir el comportamiento descrito en un conjunto de puertas lógicas que realizan la misma función. Este paso se llama síntesis lógica, y para realizarla son necesarias la descripción de nuestro circuito, la información de puertas disponibles de la tecnología que usamos e incluir las limitaciones del circuito.

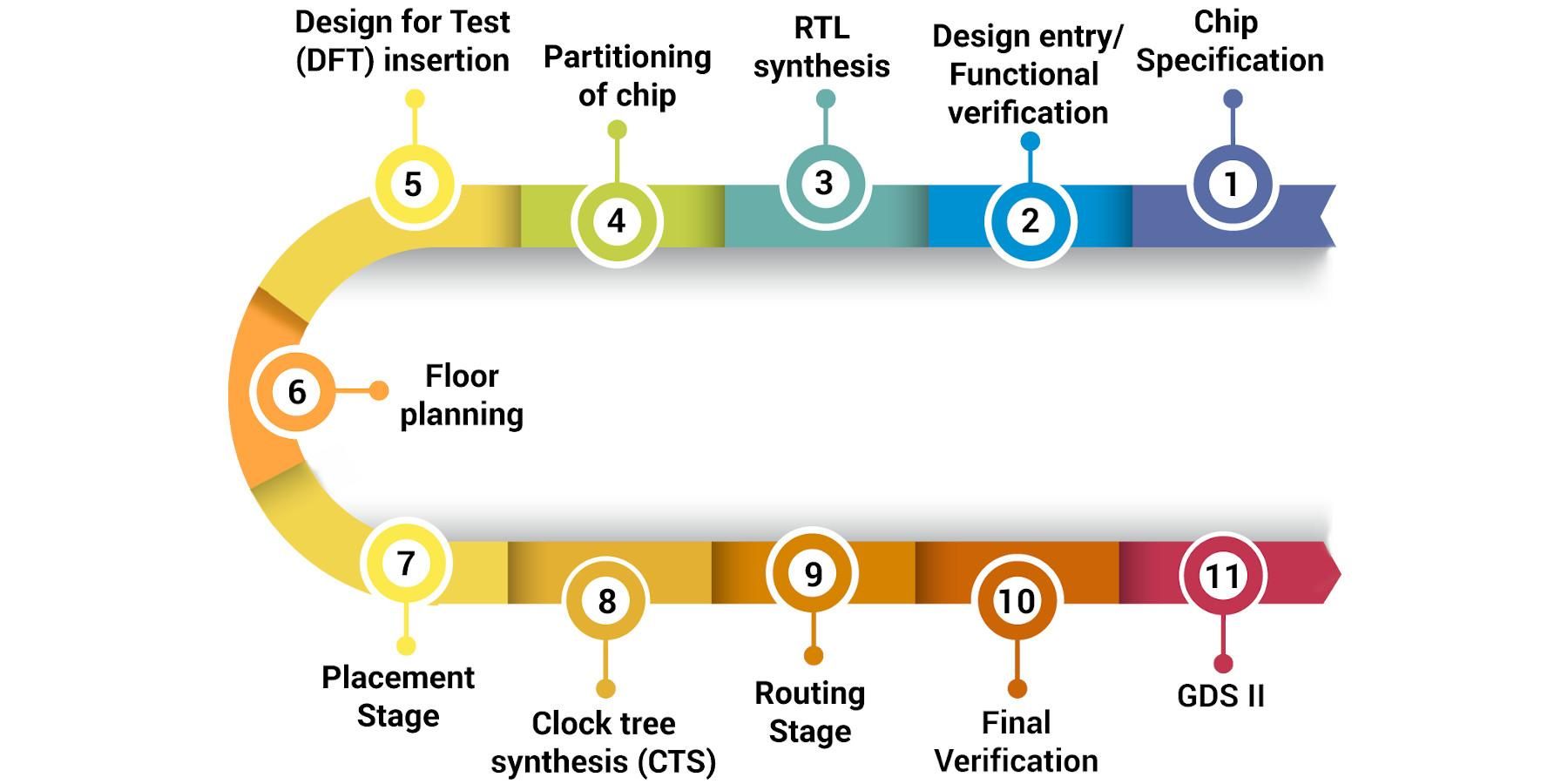

Una vez finalizada la síntesis, obtenemos un fichero, llamado "netlist", donde encontraremos el circuito digital que hemos diseñado expresado en puertas lógicas disponibles en la tecnología elegida. El siguiente paso consiste en distribuir las celdas lógicas, bloques analógicos, GPIOs y memorias en un área determinada y, además, realizar las conexiones entre ellos. Este paso se llama síntesis física, y se puede resumir, muy brevemente, en 5 etapas: Floorplan, Placement, Clock tree synthesis (CTS), Routing y Signoff o Final Verification (ver figura 2, del paso 6 al 10).

En la etapa Floorplan hacemos la distribución de nuestro SoC, el área que ocuparán los circuitos digitales, donde pondremos las memorias y GPIOs, donde pondremos los bloques analógicos y cómo alimentaremos los circuitos. En la etapa Placement, se realiza una primera disposición de las puertas lógicas para comprobar que el diseño realmente se puede realizar, considerando el espacio disponible y las limitaciones temporales que queremos conseguir. En la etapa CTS, se realiza la distribución de la red de los relojes del sistema. En la etapa Routing, se realiza la conexión física, a través de líneas de metal, de las puertas lógicas. Finalmente, la etapa Signoff sirve para cerrar el chip; aquí se ejecutan comprobaciones temporales y tecnológicas para saber si el chip cumple las limitaciones temporales que deseamos y, también, si el chip puede ser fabricado. Esta última etapa finaliza generando un archivo GDS II que, en resumen, es lo que necesita la fundición de semiconductores para fabricar el chip.

Cofinanciación del Fondo Europeo de Desarrollo Regional de la Unión Europea

El proyecto DRAC, con número de expediente 001-P-001.723, ha sido cofinanciado al 50% con 2.000.000,00 € por el Fondo Europeo de Desarrollo Regional de la Unión Europea en el marco del Programa Operativo FEDER de Cataluña 2014-2020, con el apoyo de la Generalitat de Catalunya.