El IMB-CNM desarrolla un circuito específico de lazo de seguimiento de fase para el nuevo chip Sargantana

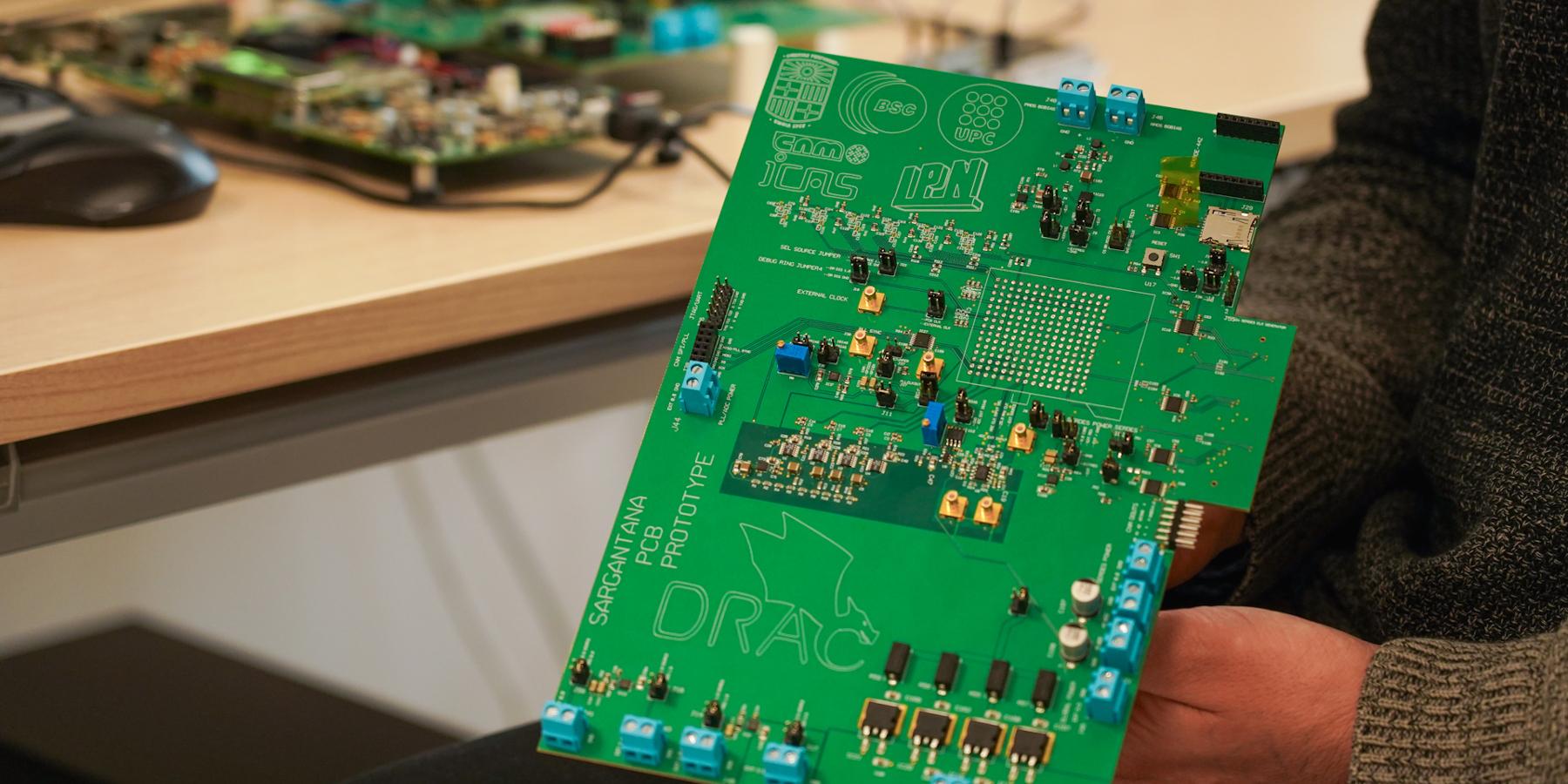

Sargantana, la nueva generación de chips de código abierto basados en procesadores avanzados RISC-V, fue presentado por el Barcelona Supercomputing Center el miércoles 20 de diciembre, en el marco del proyecto DRAC. Al igual que en los anteriores lanzamientos, el IMB-CNM ha colaborado en una parte crítica del desarrollo.

El Instituto de Microelectrónica de Barcelona (IMB-CNM-CSIC) ha desarrollado un circuito específico de lazo de seguimiento de fase o PLL (del inglés phase-locked loop) para los nuevos procesadores avanzados RISC-V del proyecto DRAC liderado por el Barcelona Supercomputing Center – Centro Nacional de Supercomputación (BSC-CNS). El BSC-CNS presentó el pasado miércoles 20 de diciembre el nuevo chip Sargantana, la tercera generación de procesadores de código abierto.

Sargantana (nombre de lagartija en aragonés y catalán) constituye la tercera generación de los procesadores Lagarto, los primeros chips de código abierto (open source) desarrollados en España, en el marco del proyecto DRAC (Designing RISC-V-based Accelerators for next generation Computers), y es uno de los chips de código abierto más avanzados de Europa a nivel académico. El nuevo Sargantana presenta una mejor prestación de rendimiento que sus dos predecesores -Lagarto Hun (2019) y DVINO (2021)- y es el primer procesador de la familia Lagarto que rompe la barrera del gigahercio en la frecuencia de trabajo.

Mientras que el RISC-V es el cerebro del procesador, el PLL desarrollado por el IMB-CNM-CSIC es el corazón del mismo, ya que es el circuito encargado de marcar su ritmo de funcionamiento. Gracias a las nuevas tecnologías es posible hacer que los núcleos de los chips trabajen a ritmos muy superiores al de las señales externas de las placas de circuito impreso donde están ensamblados. "Ello permite obtener mejores prestaciones y ofrecer rendimientos de 10 o 20 veces mayores que los circuitos que gestionan los ordenadores fuera del procesador, pero obliga a tener un PLL que permita subir el ritmo de ejecución de las instrucciones", explica Lluís Terés, investigador del grupo de Circuitos Integrados y Sistemas (ICAS).

El diseño del PLL del IMB-CNM-CSIC utiliza una frecuencia de referencia externa de 100 MHz para generar un reloj interno, programable digitalmente y sincronizado, de 1.2 GHz a 2.4 GHz, pudiéndose extender hasta los 3 GHz. De hecho, este PLL genera directamente combinaciones de frecuencias de trabajo de N/R veces 100 MHz, donde N y R son números enteros. Esto permite ofrecer un amplio abanico de ritmos de funcionamiento al procesador, que podrá adaptar la velocidad de ejecución a las cargas de trabajo y con ello optimizar su consumo de energía. El circuito desarrollado se ha integrado en el mismo chip que el núcleo RISC-V Sargantana del BSC con una tecnología CMOS de 22 nm de Global Foundries, ocupando el bloque PLL una superficie de tan solo 0,0064 mm².

Trabajo conjunto coordinado en el proyecto DRAC

En el desarrollo de Sargantana, proyecto coordinado por el BSC-CNS, ha participado personal investigador de otras universidades y centros de investigación, más allá del IMB-CNM-CSIC, como el Centro de Investigación en Computación del Instituto Politécnico Nacional de México (CIC-IPN), la Universitat Politècnica de Catalunya (UPC), la Universitat Autònoma de Barcelona (UAB), la Universitat de Barcelona (UB) y la Universitat Rovira i Virgili (URV).