El IMB-CNM desarrolla un circuito específico de lazo de seguimiento de fase para el nuevo chip Sargantana

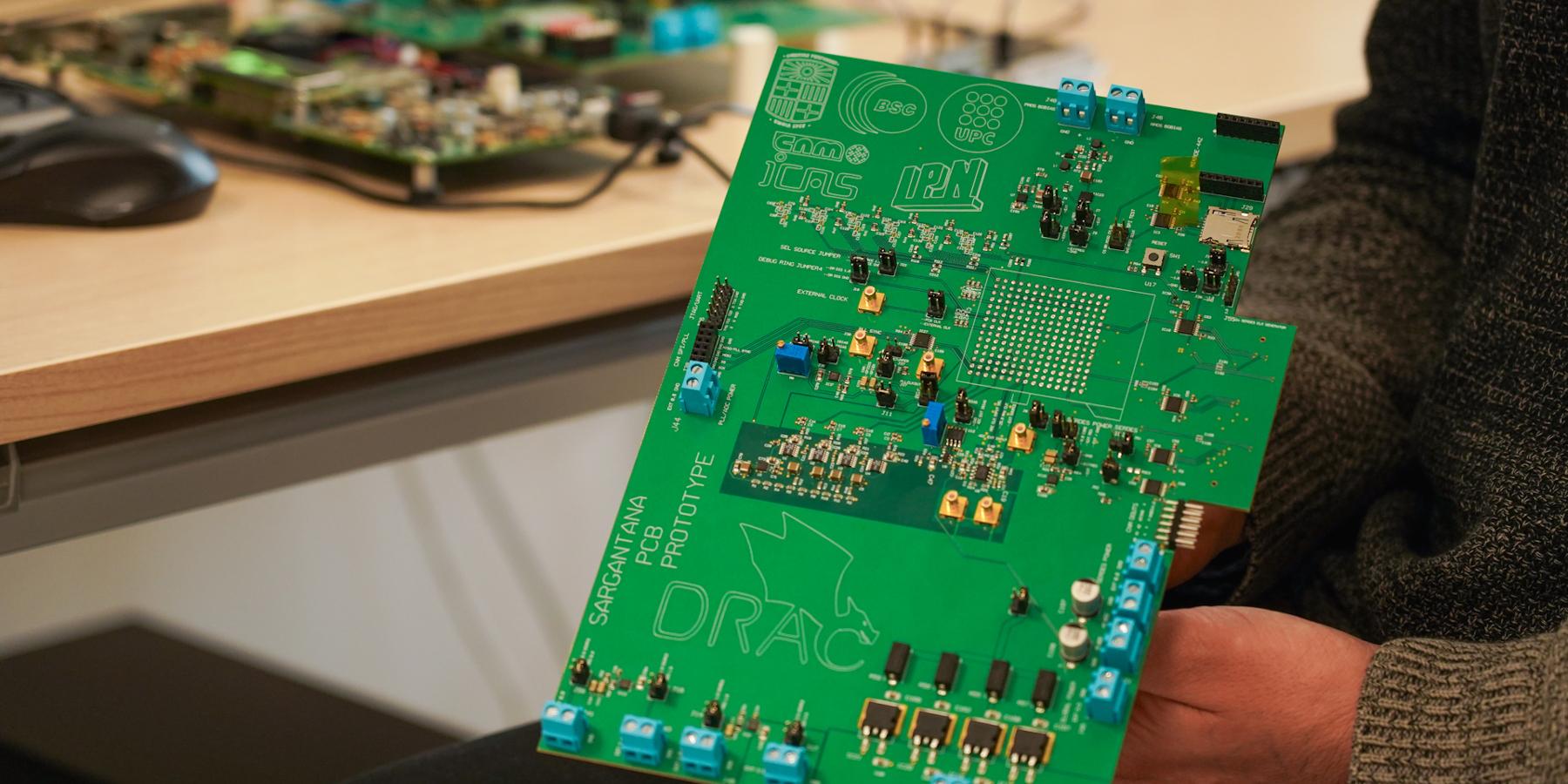

Sargantana, la nueva generación de chips de código abierto basados en procesadores avanzados RISC-V, fue presentado por el Barcelona Supercomputing Center el miércoles 20 de diciembre, en el marco del proyecto DRAC. Al igual que en los anteriores lanzamientos, el IMB-CNM ha colaborado en una parte crítica del desarrollo.

L'Institut de Microelectrònica de Barcelona (IMB-CNM-CSIC) ha desenvolupat un circuit específic de llaç de seguiment de fase o PLL (de l'anglès phase-locked loop) per als nous processadors avançats RISC-V del projecte DRAC liderat pel Barcelona Supercomputing Center – Centre Nacional de Supercomputació (BSC-CNS). El BSC-CNS va presentar dimecres passat 20 de desembre el nou xip Sargantana, la tercera generació de processadors de codi obert.

Sargantana (nom de sargantana en aragonès i català) constitueix la tercera generació dels processadors Lagarto, els primers xips de codi obert (open source) desenvolupats a Espanya, en el marc del projecte DRAC (Designing RISC-V-based Accelerators for next generation Computers), i és un dels xips de codi obert més avançats d'Europa a nivell acadèmic. El nou Sargantana presenta una millor prestació de rendiment que els seus dos predecessors -Lagarto Hun (2019) i DVINO (2021)- i és el primer processador de la família Lagarto que trenca la barrera del gigaherci en la freqüència de treball.

Mentre que el RISC-V és el cervell del processador, el PLL desenvolupat per l'IMB-CNM-CSIC és el cor d'aquest, ja que és el circuit encarregat de marcar el seu ritme de funcionament. Gràcies a les noves tecnologies és possible fer que els nuclis dels xips treballin a ritmes molt superiors al dels senyals externs de les plaques de circuit imprès on estan acoblats. "Això permet obtenir millors prestacions i oferir rendiments de 10 o 20 vegades majors que els circuits que gestionen els ordinadors fora del processador, però obliga a tenir un PLL que permeti pujar el ritme d'execució de les instruccions", explica Lluís Terés, investigador del grup de Circuits Integrats i Sistemes (ICAS).

El disseny del PLL de l'IMB-CNM-CSIC utilitza una freqüència de referència externa de 100 MHz per a generar un rellotge intern, programable digitalment i sincronitzat, d'1.2 GHz a 2.4 GHz, podent-se estendre fins als 3 GHz. De fet, aquest PLL genera directament combinacions de freqüències de treball de N/R vegades 100 MHz, on N i R són nombres enters. Això permet oferir un ampli ventall de ritmes de funcionament al processador, que podrà adaptar la velocitat d'execució a les càrregues de treball i amb això optimitzar el seu consum d'energia. El circuit desenvolupat s'ha integrat en el mateix xip que el nucli RISC-V Sargantana del BSC amb una tecnologia CMOS de 22 nm de Global Foundries, ocupant el bloc PLL una superfície de tan sols 0,0064 mm².

Treball conjunt coordinat en el projecte DRAC

En el desenvolupament de Sargantana, projecte coordinat pel BSC-CNS, ha participat personal investigador d'altres universitats i centres de recerca, més enllà de l'IMB-CNM-CSIC, com el Centre de Recerca en Computació de l'Institut Politècnic Nacional de Mèxic (CIC-IPN), la Universitat Politècnica de Catalunya (UPC), la Universitat Autònoma de Barcelona (UAB), la Universitat de Barcelona (UB) i la Universitat Rovira i Virgili (URV).