# Master Thesis (with possibility of PhD Thesis)

at the Integrated Circuits and Systems (ICAS) research group of IMB-CNM(CSIC)

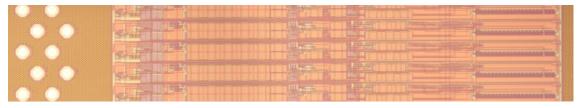

# Low-Noise Multi-Channel Read-Out Integrated Circuit for Differential Mobility Analyzers

## Description

Differential mobility analyzers (DMAs) provide ion mobility spectrometry and are highly demanded analytical instruments for the detection of explosives, chemical weapons and drugs in military and security applications. The use of a custom read-out integrated circuit (ROIC) for the A/D conversion of the ion currents can strongly improve the performance of the DMA equipment. First, the ROIC frontend can be designed for low-noise operation in order to further increase the high sensitivity of DMAs. Second, the CMOS integration of the read-out circuits can lead to portable equipments suitable for in-field applications, e.g. customs control at airports and harbors. Third, high channel count (e.g. 128 to 256) ROICs can speed up spectrometry acquisition by parallel A/D data conversion. On the other hand, ROIC implementations have to face the typical leakage issues of CMOS technologies. This work will design the complete channel IP block needed to build a 128-channel DMA ROIC in 180-nm CMOS technology. The main circuit design efforts will be focused on low-noise performance and compact channel pitch.

### **Background and skills**

- Electronic engineering or any similar curriculum covering the following topics: CMOS technology basics, MOS device modeling, analog and mixed-signal CMOS circuit design.

- Knowledge of EDA tools and HDLs for full-custom IC design.

- Capability of working as a team.

- Good spoken and written English.

### Tasks

The student will design the analog and mixed-signal parts of the channel module circuit needed for a 128-channel ROIC in a given 180-nm 1.8-V CMOS technology following the full-custom IC design methodology through Cadence EDA tools. Apart from low-noise operation and compact circuit area, the channel schematic and layout design will be optimized for its robustness against process-supply-temperature (PVT) variations. All the above tasks will be performed in the IMB-CNM lab facilities at the UAB Bellaterra Campus.

| Contact | Dr.   |

|---------|-------|

|         | 11.12 |

Dr. Lluís Terés lluis.teres@imb-cnm.csic.es Dr. Francesc Serra Graells paco.serra@imb-cnm.csic.es